-

미리보기는

3 페이지 까지 제공됩니다. -

- 공학,기술계열

-

[전자회로 설계] 전자회로 BJT-Amp 설계

-

[전자회로 설계] 전자회로 BJT-A.hwp

[전자회로 설계] 전자회로 BJT-A.hwp

- 등록인 leewk2547

- 등록/수정일 14.06.06 / 14.06.06

- 문서분량 9 페이지

- 다운로드 1

-

구매평가

판매가격 2,000원

|

|

- 같은분야 연관자료

- 보고서설명

- Gain = 20DB

Input impedance 는 1k 이상

Output impedance 는 10 이하

※ Common emitter에 다른 소자들을 추가 시킬 경우 Spec에 많은 차이를 나타내므로 대략적인 Spec을 조사해보자.

※ Dc Bias

좌측의 그림과 같이 Common emitter의 Base단의 전압은 대략 0.65V – 0.75V 정도를 걸어주게 되면 높은 Gain을 얻을 수 있다.

- 본문일부/목차

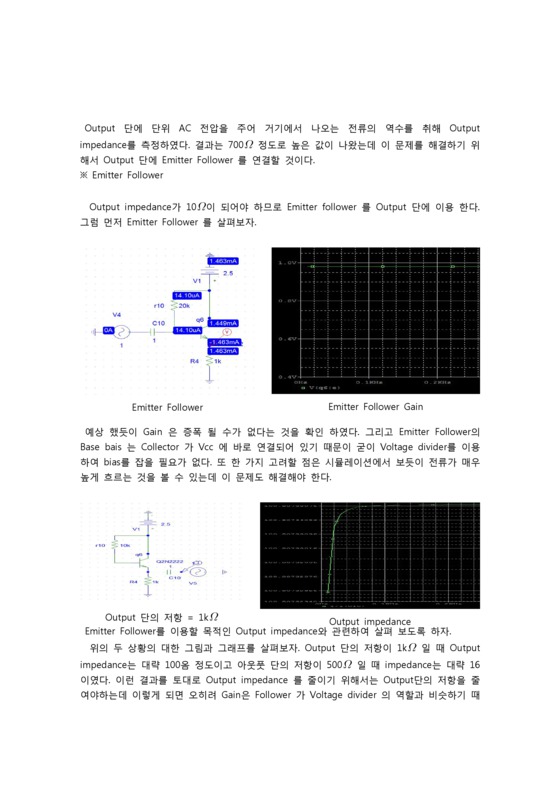

- 처음 회로 설계시 Common emitter한개로 설계를 하였는데, 목표로 하는 전력소비 최소를 맞출 수가 없었다. 원인을 분석하였더니, 우선 베이스 단자 쪽에 걸어두었던 Follower는 필요가 없었고, Gain과 In/Output impedance는 스펙을 만족하였으나 트랜지스터 자체가 동작영역이 아니었다. 따라서 고민 끝에 Common emitter 로써 2개를 연결하여서 우선은 많은 Gain을 만들었다. 그리고 Q3에 해당하는 Emitter Follower를 추가하여 아웃풋 임피던스를 낮추어 설계하였다. 그다음에 적절한 BIAS POINT를 찾기 위하여 Divider를 이용하여 베이스 전압을 687mV정도로 맞추었고, 다음으로 R3, R6의 저항 값을 조정하여서 Vcc에 흐르는 전류를 감소하면서 Gain값도 동시에 조정하였다. 그다음 R9와 C4를 추가하여 Gain에 영향을 주지 않고 Emitter Follower에 흐르는 전류를 낮추었다. 또한 C1, C2, C3 는 각 단의 트랜지스터로 빠져나가는 전류를 없애기 위해 연결 하였다. 이런 식으로 Feed-Back을 계속하여 최종적으로 스펙을 만족하면서 Power consumption을 최소화 시키는 Optimaze Point에 근접시켰다. 그 결과 맨 처음 설계했던 BJT Amp보다 Power consumption을 10배이상 줄일 수 있었다.

최종적으로 우리 조는 input-impedance 와 output-impedance를 최대한 만족시키는 선에서 제 1우선순위를 power consumption으로 맞춰진 BJT를 설계하였다. 회로를 설계하면서, 주어진 조건들을 최적의 상태(Optimized Condition)로 만든다는 것이 상당히 어렵다는 것을 느끼게 되었다. 어느 하나의 조건만 따지면 간단하게 최대 혹은 최소로 맞출 수 있지만, 여러 가지 조건들을 만족시켜야 되었기 때문에 이 조건들 간의 적절한 Trade-Off가 이루어져야 했다. 따라서 어떤 조건을 좀 더 비중 있게 두느냐에 대한 우선 순위를 먼저 정하는 것이 타당하다고 생각한다.

- 연관검색어

- #전자회로 설계

구매평가

| 구매평가 기록이 없습니다 |

- 보상규정 및 환불정책

-

· 해피레포트는 다운로드 받은 파일에 문제가 있을 경우(손상된 파일/설명과 다른자료/중복자료 등) 1주일이내 환불요청 시

환불(재충전) 해드립니다. (단, 단순 변심 및 실수로 인한 환불은 되지 않습니다.)· 파일이 열리지 않거나 브라우저 오류로 인해 다운이 되지 않으면 고객센터로 문의바랍니다.

· 다운로드 받은 파일은 참고자료로 이용하셔야 하며,자료의 활용에 대한 모든 책임은 다운로드 받은 회원님에게 있습니다.

저작권안내

보고서 내용중의 의견 및 입장은 당사와 무관하며, 그 내용의 진위여부도 당사는 보증하지 않습니다.

보고서의 저작권 및 모든 법적 책임은 등록인에게 있으며, 무단전재 및 재배포를 금합니다.

저작권 문제 발생시 원저작권자의 입장에서 해결해드리고 있습니다.

저작권침해신고 바로가기

보고서의 저작권 및 모든 법적 책임은 등록인에게 있으며, 무단전재 및 재배포를 금합니다.

저작권 문제 발생시 원저작권자의 입장에서 해결해드리고 있습니다.